Allegro PCB Design Flow

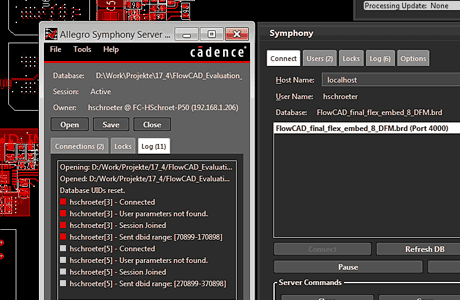

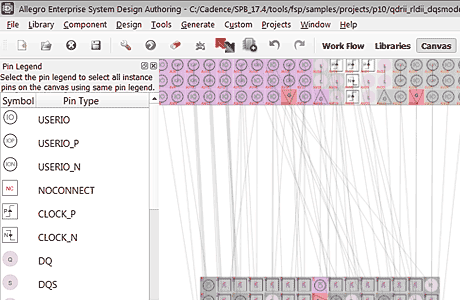

Cadence Allegro PCB Designer bringt einfache und komplexe Designs schnell vom Konzept bis zur Produktion in einem Constraint-gesteuerten Designsystem, das Funktionalität und Herstellbarkeit sicherstellt. Skalierbare Technologie ermöglicht es Designern, alle aktuellen und zukünftigen technologischen und methodischen Anforderungen an Teams, Organisationen und Projekte jeder Größe und Komplexität kostengünstig zu erfüllen. Allegro PCB Designer ermöglicht Ihnen High-Speed-Design, RF-Antennen, Flex-Schaltungen und Design for Manufacturing (DFM) Technologie.

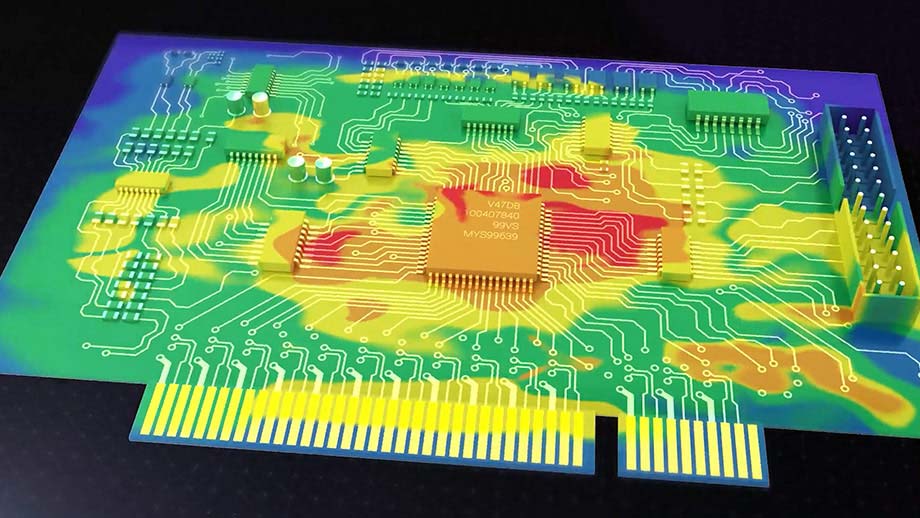

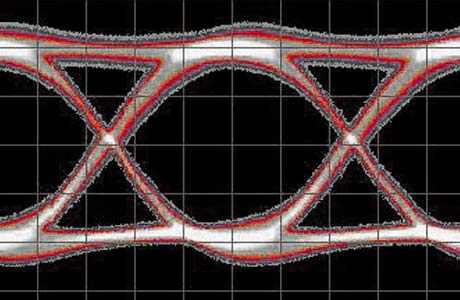

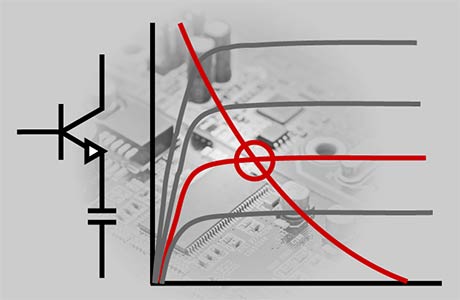

Mit der Indesign Analysis kann ein PCB Layouter eine Simulation im Hintergrund auslösen, ohne viel Wissen über Simulationen. Er erhält ein Ergebnis und kann seine Änderungen mit der vorherigen Simulation vergleichen. Auf diese Weise ist der Layouter in der Lage, die komplexesten Signalintegritätssituationen zu optimieren. Die Simulation verwendet Standardmodelle, Parameter des Datenblattes oder, falls vorhanden, Simulationsmodelle. Die Idee ist, dass selbst wenn die Indesign Analysis die Genauigkeit von Flaggschiffwerkzeugen aufgrund der vereinfachten Einrichtung nicht erreicht, immer noch 80 % der kritischen Fälle nur durch eine Optimierung des Layouts gelöst werden können. Gemeinsam mit einem Simulationsexperten können wirklich kritische Bereiche identifiziert und untersucht werden.